Jeff Draper

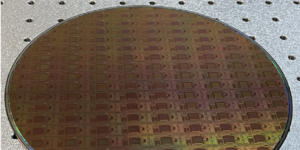

Jeff Draper and Matt French have received a contract from the Defense Advanced Research Projects Agency to aid in the creation of reliable methods to detect potential failures, inadvertent and deliberate, in integrated circuits (ICs).

The Viterbi School Information Sciences Institute researchers are participating in the Integrity and Reliability of Integrated CircuitS (IRIS) program of the DARPA Microelectronics Technology Office.

IRIS addresses a growing security problem. Integrated circuits are now embedded in every aspect of modern life and machinery, and are ubiquitous in sophisticated military equipment. But as a DARPA IRIS overview notes, the majority of such ICs “are made offshore &hellip which presents a potential risk that the parts acquired abroad will not operate only in the specified manner&hellip At present, the United States does not have a comprehensive program to certify that the ICs being used in U.S. weapons systems do not contain malicious functions.”

IRIS will foster the development of technology for deriving the functionality of an IC to determine unambiguously if malicious modifications have been incorporated, and to accurately determine the IC’s useful lifespan from a physical perspective.

Since ICs are at the core of most systems and provide the critical functionalities that differentiate systems (e.g., detection and signal processing, targeting, and processing), changes such as additions in functionality or intentionally reduced lifespan could cause faulty operation. The ISI IRIS Test Article Generation (ITAG) project that Draper and French will carry on will develop a series of designs/chips that will be used to test the integrity and reliability assessment technology under development by the IRIS program. They will deliver about ten such designs in the next three years.

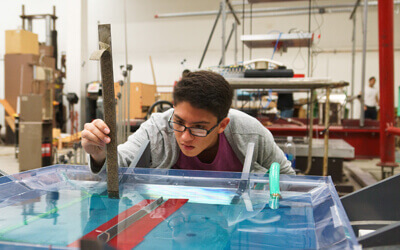

“Our role on the program,” said Draper, “is to provide test vehicles for challenging integrity and reliability issues in ICs. In the process, not only will we be conducting research into integrity and reliability issues but peripherally in other architecture areas of interest like energy vs. resilience trade-offs, network-on-chips, fine-grained computing, and similar fields.”

The current effort will benefit from results and infrastructure of a previous study by DARPA, named Trust in Integrated Circuits, in which Draper and French (left) played a key role. As DARPA noted in its published award intent, “ISI is in a unique position to conduct the subject research due to the fact they are currently providing such services in support of the Trust program. The same team, resources, access to in-house laboratories, and existing contractual/IP arrangements with vital commercial IC product/solution developers will ensure that a high quality set of test articles is produced in time to support DARPA’s impending IRIS program”

French noted that “DARPA recognized ISI’s unique role under the Trust program in our ability to combine state of the art research in circuit design with reliable low cost manufacturing provided by ISI’s MOSIS integrated chip fabrication service, while at the same time building off ISI’s legacy of developing research community infrastructure similar to such programs as ARPAnet DNS, the DETER testbed, and grid computing.”

Draper is an ISI project leader and also a research faculty member of the USC Viterbi School of Engineering’s Ming Hsieh Department of Electrical Engineering. An expert in chip architecture, he has previously participated in the creation of a number of advanced processing-in-memory chips. French is an ISI project leader with expertise in intelligent control of computer architectures and reconfigurable computing.

Published on May 22nd, 2011

Last updated on August 5th, 2021