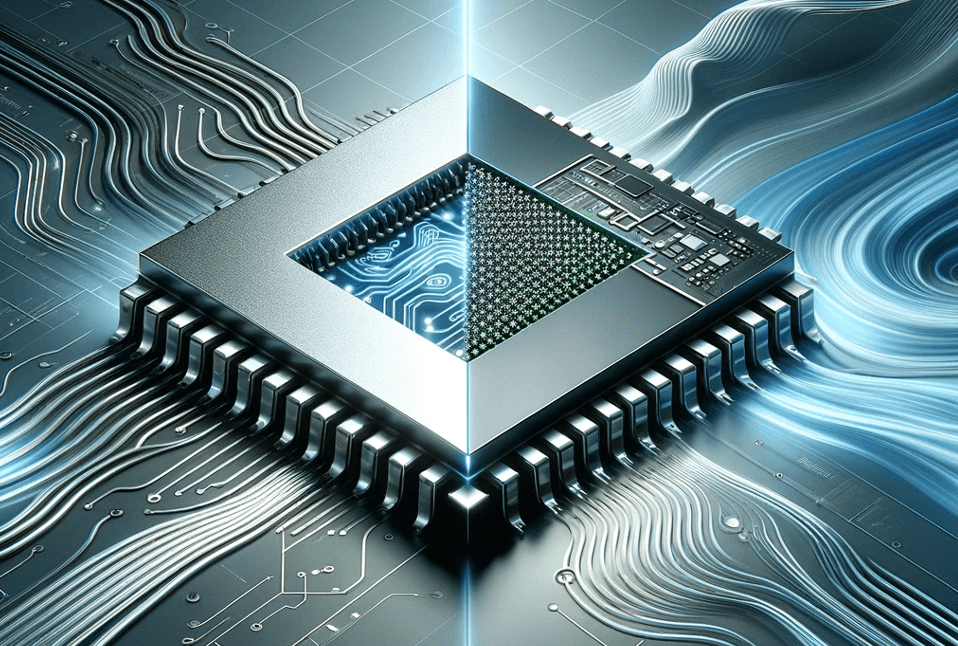

Memristor system-on-chip to power up the analog world with digital precision. (Courtesy of Tetramem Inc. This image was generated with the assistance of AI)

Our world is analog. Analog computing with analog devices is the most natural and efficient way to deal with the world, but there are issues with accuracy. Digital devices are more precise, but they use a lot of energy to do their work. So much energy, in fact, that it’s not sustainable given the amounts of data needed to power the future. What’s the solution?

J. Joshua Yang, the Arthur B. Freeman Chair Professor in the USC Ming Hsieh Department of Electrical and Computer Engineering and his team have led the way in developing a type of circuit architecture that enables low-precision analog devices to perform high-precision computing tasks.

“Compared to the digital approach, this has orders of magnitude higher efficiency, and similar precision,” Yang said.

The findings were published Thursday in the journal Science, co-authored by Yang’s students (Wenhao Song et. al) and colleagues (Mike Chen and Peter Beerel) at USC, as well as collaborators from Tetramem Inc. (Glenn Ge, Miao Hu et. al), UMass Amherst (Qiangfei Xia), and the Air Force Research Laboratory (Mark Barnell and Qing Wu).

Prof. J. Joshua Yang

The key to the increase in precision, coupled with maintaining the level of efficiency, is something Yang and the team have been working on for years: co-design of the emerging memory devices, architecture, and algorithms. They used resistance random access memory (RRAM) to demonstrate their new idea although it will work for any resistance-based memory devices, including Phase Change Memory (PCM), Ferroelectric RAM (FeRAM), and Magnetic RAM (MRAM). Such analog memory devices allow computers to process large amounts of information physically in the memories with high energy efficiency and throughput. The secret of the new design is “We use a weighted sum of multiple devices to represent one number, in which subsequently programmed devices are used to compensate for preceding programming errors,” the paper states. “With a memristor system-on-chip, we experimentally demonstrate high-precision solutions for multiple scientific computing tasks while maintaining a substantial power efficiency advantage over conventional digital approaches.”

As Yang points out, using more memristors to represent one number inevitably will increase the number of memristors needed, which fortunately is affordable given the intrinsic high scalability of memristors. After all, “there’s no free lunch,” he said. “The point is, you can in principle get the precision as high as you need even with analog computing, using our approach.”

The research further cements previous results Yang and his team have achieved with chips made by Tetramem, a startup co-founded by Yang and some of his co-authors (Miao Hu, Qiangfei Xia, and Glenn Ge), to commercialize AI acceleration technology. According to Yang, that neural processing unit (NPU) chip has the highest device precision, i.e., 11 bit/device, among all types of known memory technologies thus far. The technological leaps observed with the chip were described in research published in a Nature paper in March 2023. Such advancements at the device level hold great promise for applications in neural networks and machine learning inference. However, they still fall short of meeting the precision requirements for tasks like scientific computing and training in artificial intelligence. To bridge this gap, innovation at the circuit and architecture levels is imperative, which is exactly what has been demonstrated in this Science paper.

In addition, what also sets this development apart is its practical implementation not just in academic settings but in cutting-edge System-on-Chip (SoC) designs. These SoC chips integrate multiple memristor-based NPUs, a feat achieved by Tetramem and realized through fabrication in standard commercial foundries. This achievement marks a significant milestone, signaling the potential for widespread commercialization of analog computing solutions with both high efficiency and precision.

—

About the research: Funded by Tetramem (015542- 00001); Army Research Office (grant no. W911NF2120128 and W911NF1810268); Air Force Office of Scientific Research through the Multidisciplinary University Research Initiative program under contract no. FA9550-19-1-0213; US Air Force Research Laboratory (FA8750-22-1-0501); National Science Foundation under contract no. 2023752 and 2036359.

Published on February 22nd, 2024

Last updated on February 22nd, 2024