(Illustration: iStock)

The Nanowatt platform for Sensing, Analysis, and Computation (NaPSAC) platform, launched by the Department of Defense, aims to develop “novel in-memory computing architectures capable of transformative advances in computing accuracy, scalability, and power efficiency.”

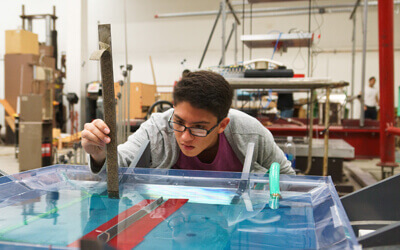

Zaijun Chen (Credit: Optica)

“The scaling of digital electronics has fallen behind the rapidly growing needs in computing power. A fundamentally different computing paradigm needs to be developed to provide scalable and efficient computing power,” said team leader Zaijun Chen, a research assistant professor of electrical and computer engineering in the USC School of Advanced Computing, a new unit of the Viterbi School. “Photonics is emerging as a promising platform.”

Chen runs the Intelligent and Quantum Photonics research group in the SAC’s Ming Hsieh Department of Electrical and Computer Engineering. Essentially, he and his team are exploring new routes for advanced computing and sensing, rather than electrons. Chen’s previous work on photonic processors has demonstrated a 100-fold improvement in computing power and energy efficiency. In July 2023 Chen published a paper in the journal Nature Photonics outlining the results.

The Defense Advanced Research Projects Agency (DARPA) has provided funding for four years to three USC co-principal investigators: Chen, Assistant Professor Mengjie Yu; and Assistant Professor Chia Wei “Wade” Hsu; as well as Dirk Englund of MIT and Edo Waks of the University of Maryland.

As the research group explained in its pitch to DARPA:

“The escalating data volume and complexity resulting from the rapid expansion of artificial intelligence, internet of things and 5G/6G mobile networks is creating an urgent need for energy-efficient, scalable computing hardware. Here we demonstrate a hypermultiplexed integrated tensor optical processor [HITOP] that performs trillions of operations per second” while reducing energy costs.

Published on April 25th, 2024

Last updated on April 25th, 2024