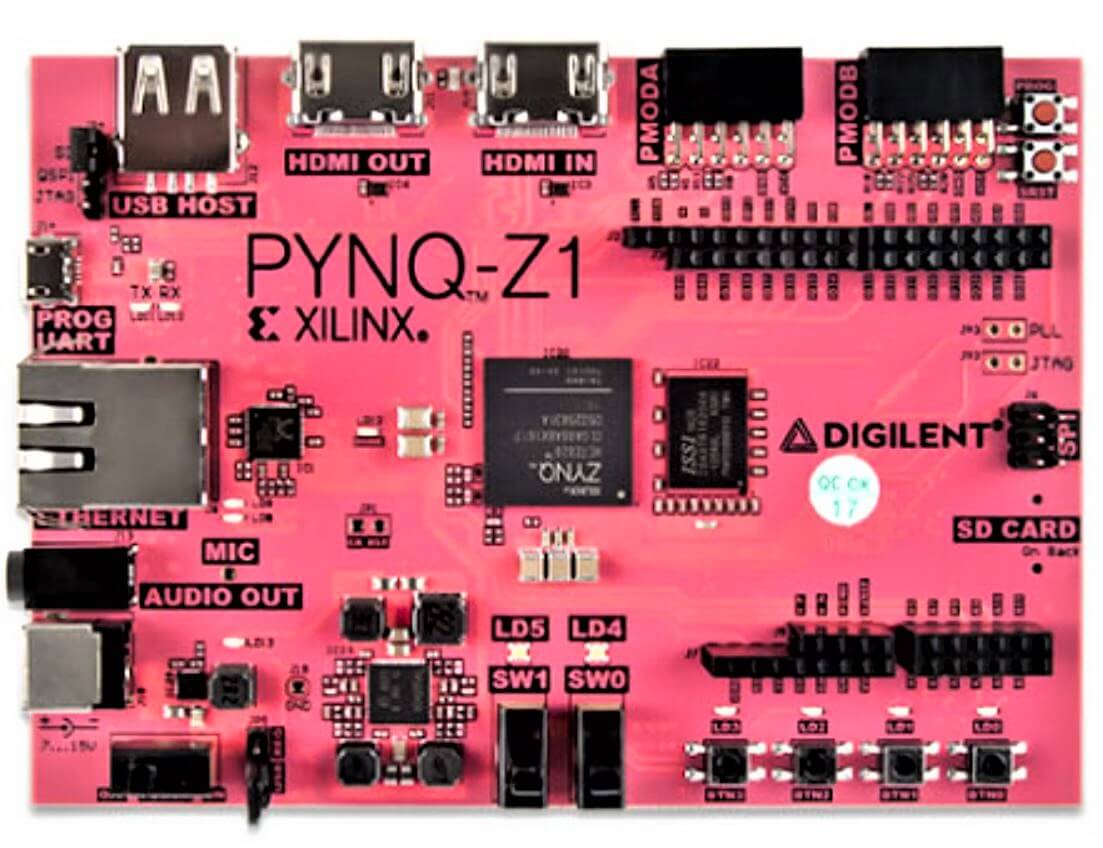

PYNQ Z1 board. Used with permission, Xilinx,Inc.

A team headed by Matthew French, a senior supervising computer scientist at the USC Information Sciences Institute, is garnering attention for a novel approach to coding field programmable gate array (FPGA) chips.

The work won Best Short Paper at the 25th IEEE Field-Programmable Custom Computing Machines symposium in May this year, and more recently was covered by the Xilinx, Inc. industry journal and by The Next Platform, a United Kingdom-based news site. “It’s one thing to think your own work is exciting,” says French. “It’s another when it reverberates through the research community.”

His team’s aim: to enable scientists to take advantage of FPGA hardware capabilities without needing to understand their complex, underlying functionality. Where conventional chips generally perform fixed functions, FPGAs are designed to be customized and reconfigured post-manufacturing. Hardware can be tailored on the fly without physically swapping out chips, which eliminates the need to create new custom interfaces for every new hardware function. The programmable chips also can offer dramatic speed gains over their conventional cousins. But FPGAs remain notoriously difficult to code and use.

Called Evaluating Rapid Application Development with Python for Heterogeneous Process-based FPGAs, the paper looks at the impact, performance and bottlenecks of leveraging the popular Python programming language with Xilinx Zynq FPGAs using PYNQ. An open-source application development environment from Xilinx, PYNQ specifically enables Python on Zynq. The appropriately rosy-hued boards are optimized for fast-start FPGA application development via Python and other features.

PYNQ’s arrival left open a couple of questions: how to integrate the hardware designs within PYNQ, and how applications would perform compared to traditional C-based approaches. Says ISI senior computer scientist Andrew Schmidt, who worked on the project with French and ISI computer scientist Gabriel Weisz, “We wanted to create something that plays really well together.”

And play they do. When Python-FPGA results were measured against hand-coded C and Python implementations, outcomes included an impressive 30-fold speedup over C and Python – a net gain that far exceeds conventional software-only implementations. That acceleration highlights the potential for Python and FPGA integration for the broader scientific research community, such as enabling scientists to receive experimental results in a few minutes rather than days. Applications eventually might include bioinformatics, deep learning, high-frequency stock trading and other complex fields.

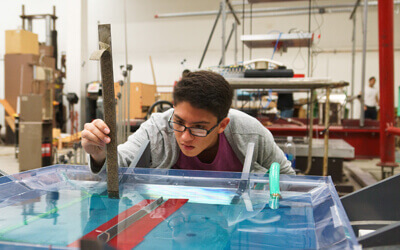

French, Schmidt and Weisz demonstrated the Python-FPGA teaming’s capability by building on their previous FPGA research, which utilized data representative of future NASA Earth and Space missions. The trio had demonstrated promising edge-detection capabilities, performance, and productivity gains, which has implications in Earth science applications, remote sensors to autonomously detect and track dynamic events, and to help rovers avoid rocks and barriers.

The team’s approach is analogous to a layer cake in which the FPGA forms the bottom layer, PYNQ the middle layer, and the applications the top layer. That addresses a thorny limitation understanding how to transfer data to and from the processors. Says Schmidt, “We’re telling programmers that they can configure the hardware however they want to, and we’ll make it more accessible to the software.”

Because French, Schmidt and Weisz readily can identify which of an application’s components are the best FPGA acceleration candidates, they can speed up only those components, achieving performance gains without disturbing the rest of the application. The trio then can leverage the large community of Python analytic tools, then rapidly insert newly accelerated code to help developers proceed faster. “This gives people a tool to very quickly identify the low-hanging fruit,” says Schmidt.

Those results also support a second aim: building a bridge between enthusiastic Python developers and FPGA researchers. “We want to show the community what’s possible, and see what will evolve,” says Schmidt. “If people can see the value, they’ll start adapting FPGAs for wider scientific work.” In the nearer term, the Python-FPGA approach could have implications for Amazon and Baidu, which have added FPGAs to their cloud computing services – elevating the need for simpler, more efficient ways to use FPGAs. And it could have yet another, equally valuable if indirect result: encouraging girls like French’s young daughter to be intrigued with STEM based on those refreshingly pink PYNQ boards.

Published on July 13th, 2017

Last updated on June 3rd, 2021